Course logo. (Image courtesy of Charles Leiserson.)

Instructor(s)

Dr. Bradley Kuszmaul

Prof. Charles Leiserson

Prof. Michael Bender

MIT Course Number

6.896

As Taught In

Spring 2004

Level

Graduate

Course Description

Course Features

Course Description

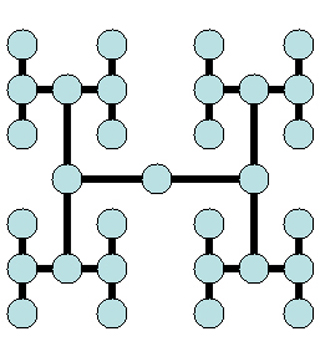

6.896 covers mathematical foundations of parallel hardware, from computer arithmetic to physical design, focusing on algorithmic underpinnings. Topics covered include: arithmetic circuits, parallel prefix, systolic arrays, retiming, clocking methodologies, boolean logic, sorting networks, interconnection networks, hypercubic networks, P-completeness, VLSI layout theory, reconfigurable wiring, fat-trees, and area-time complexity.

This course was also taught as part of the Singapore-MIT Alliance (SMA) programme as course number SMA 5511 (Theory of Parallel Hardware).